你知道石英手表为什么这么精准吗?

本文转自:https://zhuanlan.zhihu.com/p/96164213,仅供学习

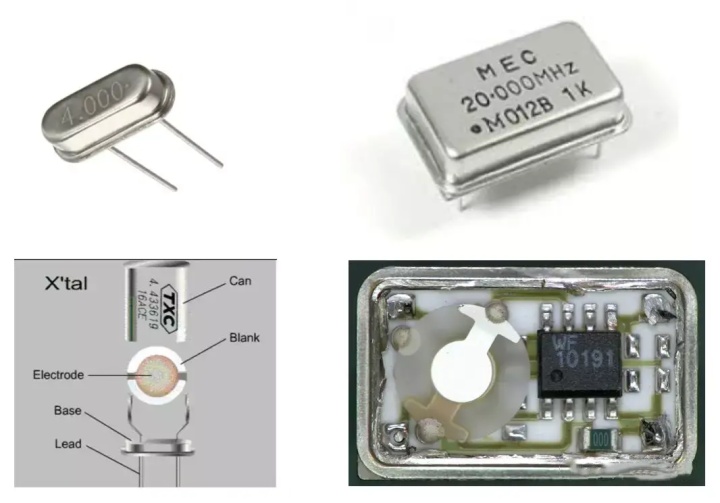

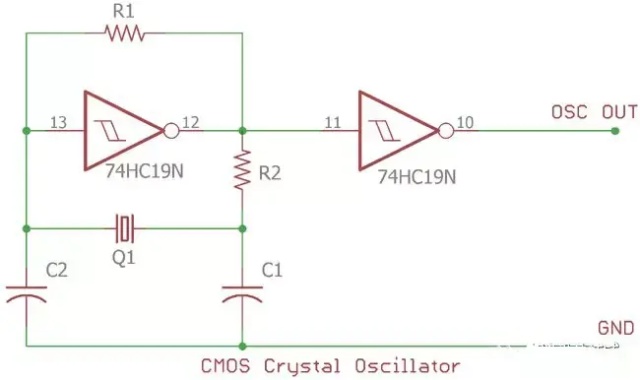

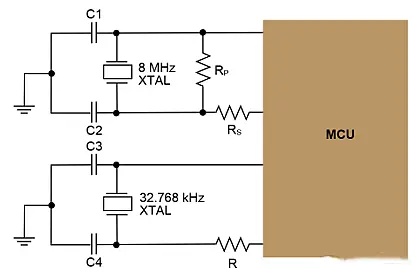

毫无疑问,这是每个硬件工程师接触的最频繁的两种器件,几乎每个工程师的器件柜里都应该有的器件,只要你用处理器,无论是8位的8051还是32位的ARM器件,总有至少两个两个管脚等着你放一颗晶体(下图左侧的器件)和俩几十pF的电容,这样MCU的心脏才能跳动起来,也才能够在时钟脉冲(像人身体的脉搏)的驱动下去执行一条条的指令。

大家要注意的是左侧的叫晶体(Crystal,也有人叫无源晶振,只有2个对称的管脚),里面的核心是一片薄薄的、具有压电效应的石英(比较便宜,且机械结构比较可靠)片,该石英片的厚度决定了振荡器的振荡频率,因此其厚度不可能无限制的薄,也就意味着石英晶体的振荡频率不可能无限制的高,一般在市场上很难买到30MHz以上的晶体,虽然有的公司能够提供到66MHz的晶体,但价格会非常的贵,因为要切割出如此高频率对应的薄石英片的成本会更高(良率比较低)。

但,你却很容易买到右侧的80MHz、100MHz的晶振(Crystal Oscillator,有人叫有源晶振,有4个管脚 - 电源、地、输出、输出使能或空),为何?因为有源晶振本质上是个内部封装了石英晶体、振荡电路、输出电平调节电路的模块,其振荡电路可以振荡在晶体的3x、5x乃至7x的谐波上,也被称为“泛音振荡器”,并能够满足你需要的电平。

石英晶体/晶振相比LC、RC、RLC振荡电路具有非常高的Q值,也就是非常高的精度和频率稳定度。我们小时候家里墙上挂的表(以及带的手表)都是机械的,校准后跑几天能差出好几分钟去,后来有了“石英钟(以及石英表)”,跑一年依然误差在一分钟以内,当时觉得非常神奇。原因就是石英的精准度和稳定度非常之高,当然有的石英表买回来就不准,你可以直接扔掉,原因就是它用的晶振振荡电路的时钟频点偏移了,也就永远调整不回来了。

有的低功耗MCU器件除了正常工作需要的比较高的时钟外,还有一个很低频率的时钟电路(比如下图中用于实时时钟的32.768KHz),能够在系统休眠(主时钟驱动的电路不工作)的情况下保持局部电路的工作。

用PLL+晶振产生更高频率的时钟信号!

石英晶体、晶振能够产生的频率比较低(能到100MHz已经不错了),而且频率很固定,如果在系统中需要非常高的频率(今天我们通信中常用的5.8GHz、CPU常用的1.8GHz是如何实现的?)而且在满足信号精度、稳定性的情况下,频率还可以非常方便地调节,如何才能实现?– 锁相环PLL。

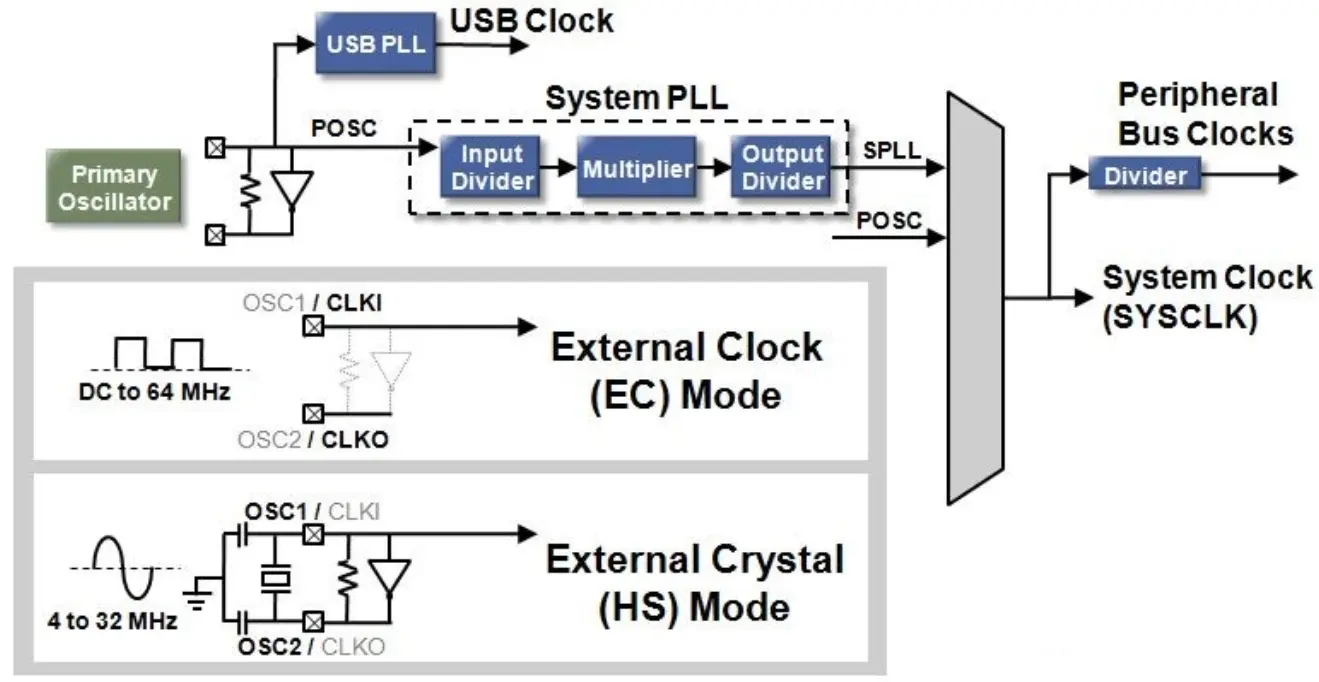

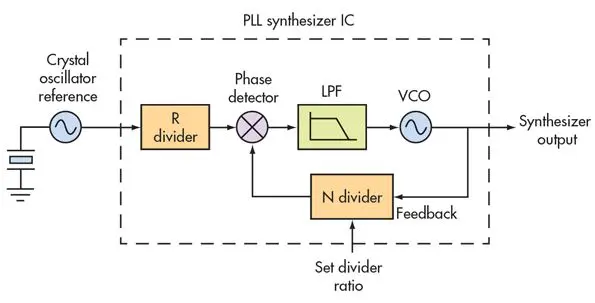

下图是PLL的方框图,细节不讲,有兴趣的自己去补,在这里只是告诉大家,PLL是基于一个外部的晶振时钟,能够先对晶振进行整数倍R分频处理,作为PLL内部的基准时钟,内部的环路可以对这个基准时钟进行N倍的倍频,因此可以得到外接晶振频率F的N/R倍的频率。

PLL不仅被广泛用在通信系统中产生方便调节的不同频点的高频率本振信号(LO),还被广泛用在处理器、FPGA、通信器件中用于生成器件内部的高速时钟。